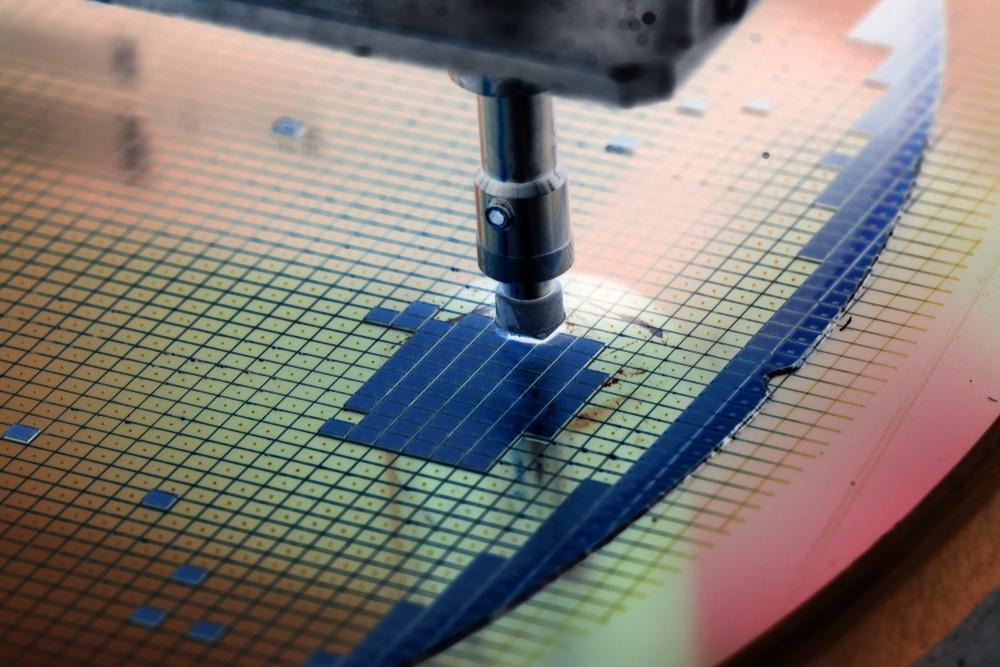

The semiconductor industry is approaching transistor scales comparable to the order of a few tens of atoms. A some point, Moore’s law, which states that the number of transistors on a microchip doubles roughly every two years, must inevitably come to a halt. This article aims to present the Single Electron Threshold Logic Gate as a possible solution to the ultimate limit of physical miniaturization.

Image Credit: Phaigraphic/Shutterstock.com

Limitations of CMOS Technology

Complementary metal-oxide-semiconductor (CMOS) technology has dominated the solid-state electronics industry for nearly half a century. Engineers in this field are used to dealing with skepticism over the technology’s prospects of further miniaturization as, decade after decade, they have been able to overcome the barriers along the way of Moore’s Law—yet this time, it is different.

The realm of physics itself is changing, and traditional modeling tools need to be reassessed. The most advanced commercial transistors at present have gate lengths anywhere between 20 to 40 nm. To put this into perspective, the inter-atomic spacing of Silicon itself is roughly 0.5 nm.

In short, transistors at this scale begin to experience quantum phenomena, resulting in deviations from the classical models that they are designed using. A concrete example is that these transistors in their off states begin to experience ‘leaks’ as electrons tunnel across the transistor channel despite the intended potential barrier, causing undesired power loss.

Anisotropic Thermal Conductors to Solve Electrical Component Overheating

A second limitation to CMOS, often overlooked due to its well-established low-cost fabrication infrastructure, is the innate redundancy associated with its logic scheme.

For each Boolean function to be implemented, a complement network of transistors associated with that function must also be implemented, essentially doubling the circuit complexity. The end of CMOS opens an opportunity to address this issue, and any solution that eliminates this redundancy could, in theory, save on size, cost, and power.

Advantages of Single Electron Threshold Logic

A significant portion of current research focuses on designing alternative logic schemes to CMOS. Researchers at the Delft University in the Netherlands proposed, back in 2001, a possible implementation of a threshold logic gate based on single-electron operations.

For a brief background, combinational logic chips at present are primarily implemented via circuits composed, under the rules of Boolean Algebra, using a set of fundamental logic gates that are functionally complete.

Image Credit: Macro photo/Shutterstock.com

These basic gates include, for example, NAND, NOR, and the set of AND, OR, and NOT gates. The concept of Threshold Logic bypasses the need for Boolean algebraic manipulations. Instead, it treats the output of a logic gate as a switch that turns on if the weighted sum of its inputs reaches or exceeds a certain gate threshold and remains off if otherwise.

In the proposal mentioned above, the single electron claim is derived from the fact that the on/off state of the output voltage is driven by the tunneling of a single electron to and from a tiny isolated metallic island sandwiched between capacitive junctions.

This concept logic gate brings many advantages and opportunities. Firstly, the single electron nature of this design takes device miniaturization to its physical limit. Additionally, Threshold Logic is capable of simulating combinational functionalities simply by setting the appropriate input weights.

This not only avoids the complementary transistor networks associated with CMOS, but also eliminates the need to construct Boolean logic circuits for complex combinational gates. Such drastic reductions in redundancies and circuit depth benefit from cutting down on size, power, and time delays.

The Challenges Ahead for Single Electron Devices

In practice, nano-systems relying on quantum phenomena are very sensitive, making them prone to random background charges. Fabricating a single-electron device in a lab is not a trivial task, and much experimental data is still required to augment the current theoretical models used for device design.

On top of this, it is an innate signature of quantum mechanics that there exists a trade-off between small scale and low energy. Current single-electron devices must operate at very low temperatures, making this technology challenging to commercialize.

Finally, a significant challenge for the industry is to devise a process for cost-effective mass production. CMOS currently has a well-established infrastructure, which there exists a minimal economic incentive for it to be replaced. However, this last point could soon change within this decade as CMOS struggles to keep up with Moore’s Law, and the semiconductor industry will be forced to adopt a new paradigm.

References and Further Reading

R. Cavin, P. Lugli, and V. Zhirnov, (2012). Science and Engineering Beyond Moore’s Law, pp. 2-10, https://www.researchgate.net/publication/238594798_Science_and_Engineering_Beyond_Moore's_Law

C. Lageweg, S. Cotofana, and S. Vassilladis, (2001). A Linear Threshold Gate Implementation in Single Electron Technology IEEE Computer Society Workshop on VLSI, pp. 93-98. https://www.sciencedirect.com/science/article/pii/S221201731300594X

S. Muroga, Threshold Logic and Its Applications, Wiley and Sons Inc.,New York, 1971. https://www.scirp.org/(S(oyulxb452alnt1aej1nfow45))/reference/ReferencesPapers.aspx?ReferenceID=2138383

Disclaimer: The views expressed here are those of the author expressed in their private capacity and do not necessarily represent the views of AZoM.com Limited T/A AZoNetwork the owner and operator of this website. This disclaimer forms part of the Terms and conditions of use of this website.