Jun 19 2008

At the VLSI Symposium, IMEC reports an improved performance for its planar CMOS using hafnium-based high-k dielectrics and tantalum-based metal gates for the 32nm CMOS node. The inverter delay advanced from 15ps to 10ps. IMEC also simplified its high-k/metal gate process by decreasing the number of process steps from 15 to 9.

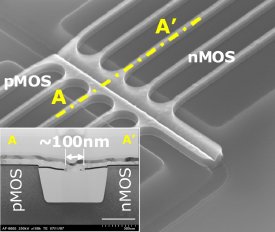

SEM and x-TEM of nMOS/pMOS boundary in ring oscillator.

SEM and x-TEM of nMOS/pMOS boundary in ring oscillator.

High-performance (low-Vt) high-k/metal-gate CMOS has recently been achieved by applying a thin dielectric cap between the gate dielectric and metal gate. Both gate-first and gate-last integration schemes have proven to be successful. While the gate-last scheme is now introduced in production for high-performance products, the gate-first option remains attractive for low-cost applications if its complexity can be reduced to the standard CMOS process flow. One of the possibilities for gate first is a dual-metal dual-dielectric process flow using mostly hard masks to pattern nMOS and pMOS regions selectively.

By applying conventional stress boosters to its gate-first dual-metal dual-dielectric high-k/metal gate CMOS, IMEC increased the performance of nMOS and pMOS transistors with 16% and 11% respectively. This results in an inverter delay improved from 15ps to 10ps. For the first time, the compatibility of conventional stress memorization techniques with high-k/metal gate has been demonstrated.

Also, IMEC has simplified the process complexity from dual-metal dual-dielectric to single-metal dual-dielectric by using soft-mask processes and wet removal chemistry. The process reduces the complexity by 40% or 6 steps compared to dual-metal dual-dielectric. It also allows simpler gate-etch profile control and it offers better prospects for scaling.

And IMEC proved that the use of La and Dy capping layers do not show any reliability issues.

These results were obtained in collaboration with IMEC’s (sub-)32nm CMOS core partners including Infineon, Qimonda, Intel, Micron, NXP, Panasonic, Samsung, STMicroelectronics, Texas Instruments and TSMC, and IMEC’s key CMOS partners including Elpida and Hynix.