Jun 19 2019

Within the framework of JST PRESTO program, Masaharu Kobayashi, associate professor at the Institute of Industrial Science, the University of Tokyo, used ferroelectric-HfO2 and ultrathin IGZO channel to design a ferroelectric FET (FeFET).

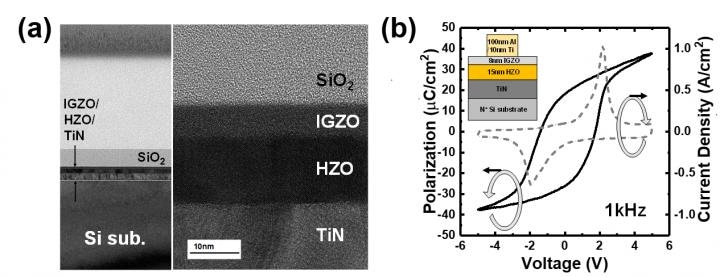

(a) Cross-sectional TEM image of a TiN/HfZrO2/IGZO capacitor. Each layer was uniformly formed. HfZrO2 layer is uniformly crystallized having ferroelectric phase. (b) Measured polarization charge versus voltage of a TiN/HfZrO2/IGZO capacitor. Clear ferroelectricity was confirmed. (Image credit: Masaharu Kobayashi)

(a) Cross-sectional TEM image of a TiN/HfZrO2/IGZO capacitor. Each layer was uniformly formed. HfZrO2 layer is uniformly crystallized having ferroelectric phase. (b) Measured polarization charge versus voltage of a TiN/HfZrO2/IGZO capacitor. Clear ferroelectricity was confirmed. (Image credit: Masaharu Kobayashi)

The researcher has demonstrated not just an almost perfect subthreshold swing (SS) but also mobility greater than polysilicon channel.

FeFET is a potential memory device owing to its properties such as high speed, low power, and high capacity. Following the discovery of CMOS-compatible ferroelectric-HfO2 material, FeFET has been gaining considerable focus like never before. A 3D vertical stack structure has been suggested for even more memory capacity.

In general, although polysilicon has essentially been used as a channel material in a 3D vertical stack structure, it has extremely low mobility in the nanometer-thick region because of extrinsic defects and grain boundaries. In addition, polysilicon develops a low-k interfacial layer with ferroelectric-HfO2 gate insulator. Consequently, there is a voltage loss and charge trapping, respectively leading to low-voltage operation hindrance and reliability degradation.

In this research, the scientists proposed a ferroelectric-HfO2-based FeFET using ultrathin IGZO channel for resolving this issue. IGZO is a metal-oxide semiconductor and is capable of preventing the formation of low-k interfacial layer with ferroelectric HfO2 gate insulator. Furthermore, as IGZO is N-type semiconductor and generally used in junctionless transistor operation, charge trapping actually experienced in the inversion mode operation could potentially be eliminated.

The researchers first analyzed the thickness of an optimum IGZO channel in a systematic manner. SS reduced and threshold voltage (Vth) increased with a decrease in IGZO thickness. In order to achieve steep SS and normally off operation, 8 nm was selected.

The researchers then developed TiN/HfZrO2/IGZO capacitor, in which HfZrO2 is the ferroelectric layer. Cross-sectional TEM image reveals the uniform formation of each layer. GIXRD spectrum was observed and confirmed the presence of ferroelectric phase. The researchers used electrical characterization and confirmed evident ferroelectric property with IGZO capping on HfZrO2.

It is worth noting that in the existing device model, back-gate is essential for the buried oxide to set body potential. Using technology computer-aided design (TCAD simulation), it was confirmed that in the absence of back-gate, body potential fluctuates and voltage cannot be satisfactorily applied on ferroelectric-HfO2 gate insulator.

According to this device design, the researchers developed a FeFET using ferroelectric-HfO2 and ultrathin IGZO channel. The measured drain current versus gate voltage after applying write-and-erase pulse voltages exhibited a memory window of 0.5 V and nearly ideal SS of 60 mV/dec. Moreover, field-effect mobility was approximately 10 cm2/V s, which can be greater than that of polysilicon of the same thickness.

The findings of this research pave the way to realize low-voltage and highly dependable FeFET with 3D vertical stack structure, facilitating ultralow-power Internet of Things (IoT) edge devices, deployment of a highly advanced network system, and offering more strategic social services using big data.