Dec 10 2018

A 3D transistor measuring less than half the size of present-day’s smallest commercial models has been fabricated by scientists from MIT and the University of Colorado. To accomplish that, they formulated a unique microfabrication method that alters semiconductor material atom by atom.

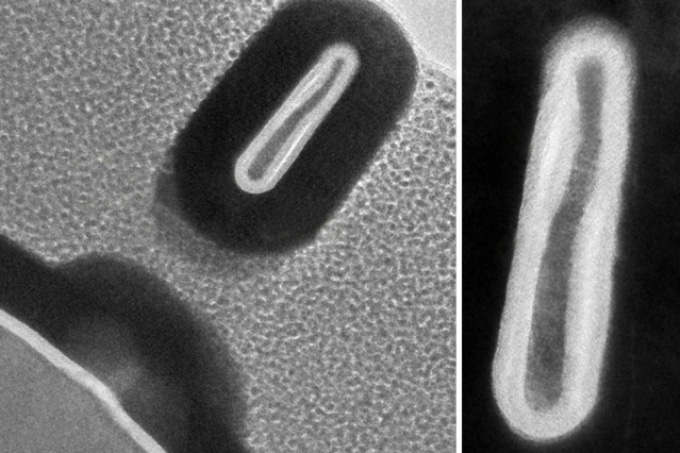

Using a new manufacturing technique, MIT researchers fabricated a 3D transistor less than half the width of today’s slimmest commercial models, which could help cram far more transistors onto a single computer chip. Pictured is a cross-section of one of the researchers’ transistors that measures only 3 nm wide. (Courtesy of the researchers)

Using a new manufacturing technique, MIT researchers fabricated a 3D transistor less than half the width of today’s slimmest commercial models, which could help cram far more transistors onto a single computer chip. Pictured is a cross-section of one of the researchers’ transistors that measures only 3 nm wide. (Courtesy of the researchers)

The inspiration behind the research was to carry on with Moore’s Law, an observation put forth in the 1960s that the number of transistors on an integrated circuit doubles about every two years. To follow this “golden rule” of electronics, scientists are continually discovering ways to pack as many transistors as possible onto microchips. The latest trend is 3D transistors that stand vertically, similar to fins, and measure about 7 nm across—tens of thousands of times thinner than a human hair. Tens of billions of these transistors can be fitted on a single microchip, which is roughly the size of a fingernail.

As illustrated in a paper presented at this week’s IEEE International Electron Devices Meeting, the scientists altered a newly invented chemical-etching method, called thermal atomic level etching (thermal ALE), to facilitate precision modification of semiconductor materials at the atomic level. Using that method, the scientists fabricated 3D transistors that are as narrow as 2.5 nm and more efficient than their commercial equivalents.

Similar atomic-level etching techniques are used today; however, the new method is more precise and produces better-quality transistors. Furthermore, it repurposes a widely used microfabrication tool used for depositing atomic layers on materials, meaning it could be quickly integrated. This could enable computer chips with much more transistors and superior performance, the scientists say.

“We believe that this work will have great real-world impact,” says first author Wenjie Lu, a graduate student in MIT’s Microsystems Technology Laboratories (MTL). “As Moore’s Law continues to scale down transistor sizes, it is harder to manufacture such nanoscale devices. To engineer smaller transistors, we need to be able to manipulate the materials with atomic-level precision.”

Collaborating with Lu on the paper are: Jesus A. del Alamo, a professor of electrical engineering and computer science and an MTL researcher who leads the Xtreme Transistors Group; recent MIT graduate Lisa Kong ’18; MIT postdoc Alon Vardi; and Jessica Murdzek, Jonas Gertsch, and Professor Steven George of the University of Colorado.

Atom by atom

Microfabrication comprises of deposition (growing film on a substrate) and etching (engraving patterns on the surface). To make the transistors, the substrate surface is exposed to light through photomasks with the shape and structure of the transistor. All material exposed to light can be etched away using chemicals, while material hidden behind the photomask stays.

The advanced methods for microfabrication are known as atomic layer deposition (ALD) and atomic layer etching (ALE). In ALD, two chemicals are placed onto the substrate surface and react with one another in a vacuum reactor to develop a film of desired thickness, one atomic layer at a time.

Traditional ALE methods use plasma with extremely energetic ions that strip away individual atoms on the material’s surface. But these result in surface damage. These techniques also expose the material to air, where oxidization causes further defects that obstruct performance.

Thermal ALE, invented in 2016 by the University of Colorado team, is a method that closely looks like ALD and relies on a chemical reaction called “ligand exchange.” In this approach, an ion in one compound known as a ligand—which binds to metal atoms—gets swapped by a ligand in a different compound. When the chemicals are purged away, the reaction makes the replacement ligands to gradually remove individual atoms from the surface. Still in its early stages, thermal ALE has, thus far, only been employed to etch oxides.

In this new research, the scientists altered thermal ALE to function on a semiconductor material, using the same reactor reserved for ALD. They used an alloyed semiconductor material, known as indium gallium arsenide (or InGaAs), which is more and more being praised as a faster, more efficient substitute to silicon.

The scientists exposed the material to hydrogen fluoride, the compound used for the original thermal ALE work, which develops an atomic layer of metal fluoride on the surface. Then, they poured in an organic compound known as dimethylaluminum chloride (DMAC). The ligand-exchange process takes place on the metal fluoride layer. When the DMAC is purged, individual atoms follow.

The method is repeated over numerous cycles. In a separate reactor, the team then deposited the “gate,” the metallic element that regulates the transistors to switch on or off.

In experiments, the scientists stripped away just .02 nm from the material’s surface at a time.

You’re kind of peeling an onion, layer by layer. In each cycle, we can etch away just 2 percent of a nanometer of a material. That gives us super high accuracy and careful control of the process.

Wenjie Lu, Study First Author and Graduate Student, Microsystems Technology Laboratories (MTL), MIT.

Since the method is very similar to ALD, “you can integrate this thermal ALE into the same reactor where you work on deposition,” del Alamo says. It merely requires a “small redesign of the deposition tool to handle new gases to do deposition immediately after etching. … That’s very attractive to industry.”

Thinner, better “fins”

Using the method, the scientists fabricated FinFETs, 3D transistors used in a number of today’s commercial electronic devices. FinFETs comprise of a thin “fin” of silicon, standing vertically on a substrate. The gate is basically wrapped around the fin. Due to their vertical shape, anywhere from 7 billion to 30 billion FinFETs can be packed onto a chip. As of this year, Qualcomm, Apple, and other tech companies have started using 7-nm FinFETs.

Most of the scientists’ FinFETs measured under 5 nm in width—a preferred threshold across industry—and approximately 220 nm in height. Furthermore, the method restricts the material’s exposure to oxygen-caused flaws that render the transistors less efficient.

The device performed nearly 60% better than traditional FinFETs in “transconductance,” the scientists state. Transistors turn a small voltage input into a current supplied by the gate that switches the transistor on or off to process the 1s (on) and 0s (off) that drive computation. Transconductance measures how much energy is needed to convert that voltage.

Restricting defects also leads to a higher on-off contrast, the scientists say. Preferably, you want high current flowing when the transistors are on, in order to manage heavy computation, and virtually no current flowing when they are off, to conserve energy.

That contrast is essential in making efficient logic switches and very efficient microprocessors. So far, we have the best ratio [among FinFETs].

Jesus A. del Alamo, Professor of Electrical Engineering and Computer Science and Head of MTL’s Xtreme Transistors Group, MIT.